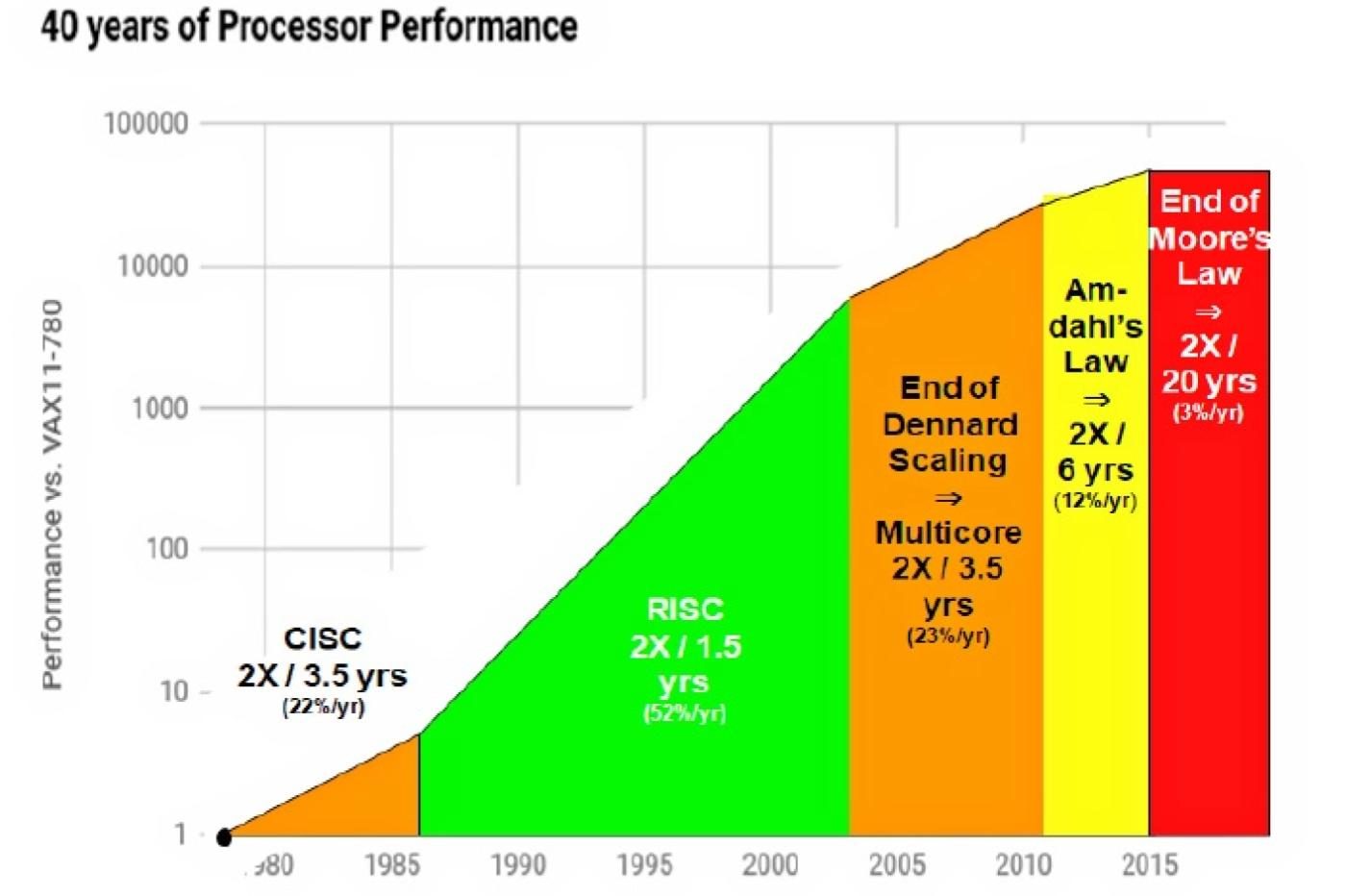

À l’époque de la montée en puissance de l’informatique, tout le monde ne jurait que par la Loi de Moore popularisée par l’ingénieur du même nom. Elle stipule qu’avec l’avancement de la technologie, le nombre de transistors (ces petites sous-unités à la base de l’architecture d’un ordinateur) dans un même circuit intégré est amené à doubler tous les deux ans, ce qui se traduit par une montée en puissance rapide des machines.

Mais contrairement à ce que suggère son nom, il ne s’agit pas d’une « loi » à proprement parler, mais d’une simple observation empirique. Or, le paysage technologique a bien changé depuis la prophétie de Moore ; depuis plusieurs années, on constate un ralentissement significatif de cette tendance.

Les causes de ce ralentissement sont encore peu claires et potentiellement très nombreuses. ON peut notamment citer les progrès fulgurants du versant logiciel, notamment avec l’explosion de l’IA ; aujourd’hui, il est possible d’atteindre des puissances calculatoires très importantes avec moins de matériel qu’à l’époque. Multiplier le nombre de transistors n’est donc plus aussi intéressant.

De plus, les procédés de fabrication deviennent extrêmement pointus ; plus on s’approche des limites physiques des procédés de fabrication, notamment en termes de miniaturisation, plus il est difficile de maintenir ce rythme d’innovation effréné. On peut aussi citer la pandémie et la pénurie de semiconducteurs qui ont pesé de tout leur poids sur les chaînes logistiques.

Utiliser le volume au lieu de miniaturiser à outrance

La loi de Moore serait-elle donc déjà morte et enterrée ? Pas forcément, selon IBM. Le géant de l’informatique s’est associé aux Japonais de Tokyo Electron pour développer une nouvelle technique de production de puces 3D ; les chercheurs considèrent qu’elle pourrait simplifier la chaîne logistique au point de remettre cette notion sur le devant de la scène.

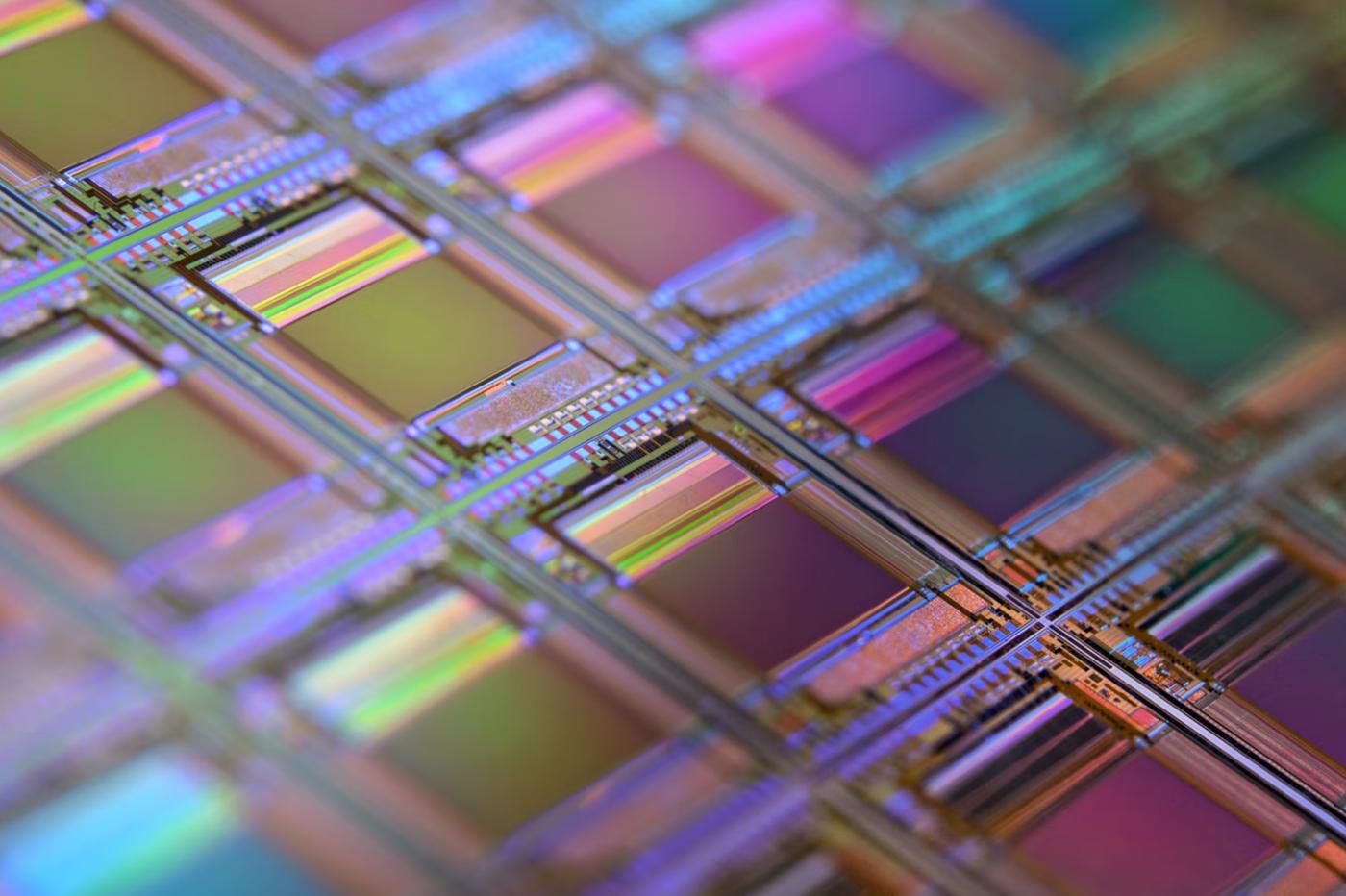

Sur une puce standard, les transistors sont disposés à plat sur un même plan 2D. Dans une puce 3D, ils sont empilés et connectés les uns sur les autres pour augmenter drastiquement la quantité de transistors dans un volume donné. De quoi dépasser le cadre de la loi de Moore qui raisonne en termes de surface, soit avec une dimension de moins.

Ce concept de chip 3D n’est pas nouveau. Tous les géants du secteur, à commencer par Intel, s’y intéressent déjà (voir la vidéo ci-dessus). Mais pour l’instant, il est encore réservé à des applications extrêmes et très spécialisées ; les intégrateurs s’en servent par exemple pour produire de la mémoire vive ultrarapide destinée aux supercalculateurs.

S’ils brillent encore par leur absence sur le segment grand public, c’est que le procédé de fabrication est très compliqué. C’est déjà difficile d’agencer des tas de minuscules transistors sur une surface, mais ça l’est encore davantage en trois dimensions.

Un nouveau procédé de fabrication

Traditionnellement, les puces sont d’abord fixées sur un support en verre. Cela permet de la renforcer pour s’assurer qu’elle survivra au processus de fabrication. Le problème, c’est qu’au bout du processus, il faut aussi retirer cette couche de verre à l’aide de lasers UV.

Le processus fonctionne très bien et est déjà maîtrisé par l’industrie pour les puces standard. Mais la présence de cette plaque de verre représente tout de même une grosse contrainte. Cela implique de très nombreuses précautions pour s’assurer que la puce n’a pas été endommagée ; et pour l’instant, cette approche reste donc incompatible avec une production de puces 3D à grande échelle.

Les chercheurs ont donc choisi une autre approche. Au lieu d’utiliser un support en verre, ils ont misé sur une plaque en silicium. Là encore, c’est une technique qui existe déjà. Elle a l’avantage d’être beaucoup plus pratique à l’échelle industrielle. Pourtant, elle est rarement utilisée. Car selon IBM, le processus de séparation nécessite l’emploi d’une force physique qui peut introduire de nombreux défauts de fabrication.

C’est là que réside la nouveauté des travaux d’IBM et de TEL. Après quatre ans d’efforts, ils ont réussi à développer un nouveau module qui permet de séparer la puce de son support à l’aide d’un laser infrarouge. Celui-ci n’affecte pas du tout le silicium ; cela permet de préserver l’intégrité parfaite de la puce, et par extension de débloquer l’utilisation de cette technologie pour produire des puces 3D à grande échelle.

Cap sur l’informatique de demain

La technologie désormais bien en place, les deux partenaires vont commencer à explorer le versant industriel de cette approche. « Nous allons montrer comment ce procédé pourrait être intégré à une chaîne de fabrication de semiconducteurs, et ainsi démontrer que notre processus est compatible avec une chaîne de production de puces 3D complètes », explique le communiqué.

Cela ne signifie pas que vous pourrez bientôt remplacer le processeur de votre ordinateur par un CPU 3D, loin de là. Cette approche est encore très expérimentale et bien loin de débarquer sur le segment grand public. Selon toute vraisemblance, il faudra encore patienter de longues années.

Mais ces structures 3D ressemblent de plus en plus à l’évolution logique et naturelle des puces actuelles. À chaque fois qu’une entreprise présente des progrès significatifs sur cette question, nous nous rapprochons donc un petit peu plus du prochain grand paradigme de l’informatique. Il sera donc intéressant de suivre l’évolution de cette technologie qui permettra peut-être à la loi de Moore de renaître de ses cendres.

🟣 Pour ne manquer aucune news sur le Journal du Geek, abonnez-vous sur Google Actualités et sur notre WhatsApp. Et si vous nous adorez, on a une newsletter tous les matins.

Après lecture de la source je suppose que l’auteur de l’article n’a pas compris grand chose, mon commentaire ci-dessous est donc obsolète mais je le laisse quand même à titre informatif…

Bonjour,

Pour compléter et nuancer votre article les transistors “type 3D”, de ce que l’on comprend dans l’article, rentre en phase de production industrielle d’ici fin de l’année 2022 / début 2023 chez TSMC (autrement appelé FinFet) en 3nm.

Ensuite pour 2025 (plutôt 2027 avec le retard), TSMC va lancer en production de masse du 2nm en nanosheet pour palier aux limites de la 3D qui sont trop importantes pour augmenter les finesses de gravure.

Pour faire simple, ils vont empiler les transistosr les uns sur les autres. Pour ce process, les outils de photolitogravure sont déjà prêt et en fabrication chez le numéro 1 (ASML) afin de lancer une production industrielle d’ici la.

Pour finir la “loi” de moore pourrais toujours être applicable… Chez TSMC notamment il travail sur du Cfet qui est un autre “arrangement-architecture” du transistor sur.

PS : Samsung lance déjà en production industrielle du MBCfeet en production de masse mais sur du 3nm (je passe les détails des “nanomètres” qui sont différents entre les fondeurs).

NOTA : L’article d’IBM, source de celui-ci, traite du développement des transistors type “MBCfeet/nanosheet” dans le but de rattraper “ses concurrents”. Il cherche une autre méthode pour empiler les uns sur les autres les transistors (chaque fondeur à sa technologie breveté).

Suffit de mettre du papier sulfurisé pour pas que ça colle…. La solution était tellement simple 🙂